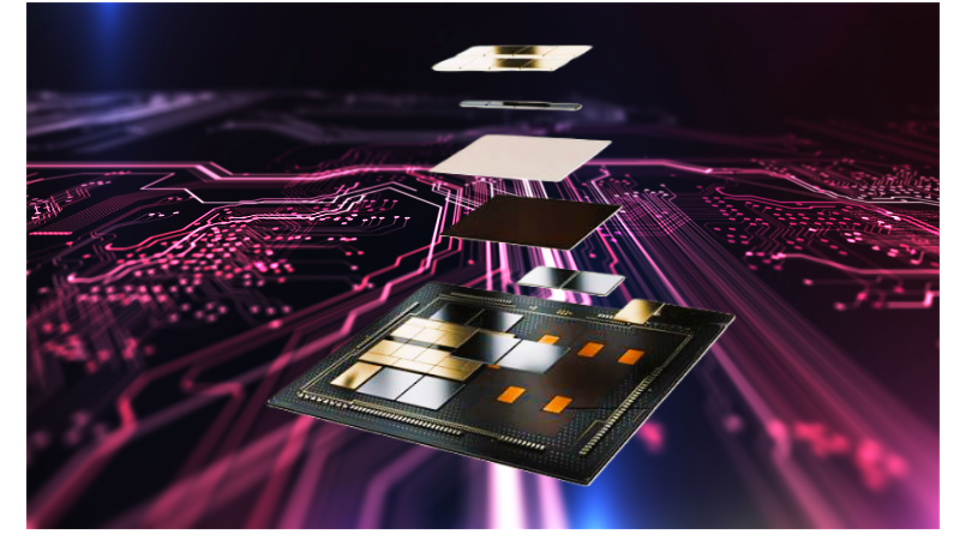

Intel’s Ponte Vecchio GPU is an example of the future of all SoCs using many heterogeneous chiplets

Intel/TIRIAS Research

Discussions about CPUs often frame one instruction set architecture (ISA) against another—x86 vs. Arm, Arm vs. RISC-V, and so on. However, it’s common to use multiple CPU architectures in a single system, whether that is a single system-on-chip (SoC) or a larger electronics platform, like a PC, car or even a data center. Throughout the history of the electronics industry, there has never been just one CPU architecture option because no two processing workloads are the same.

Tirias Research has consulted for AMD, Arm, Intel, MIPS, Qualcomm and other companies mentioned in this article.

Each architecture has its advantages and disadvantages in terms of software support, complexity, flexibility, power and cost. As a result, it is common practice to leverage multiple CPU architectures to handle different workloads or functions, just as it is common to use different accelerators, such as digital signal processors (DSPs), graphics processing units (GPUs), neural processing units (NPUs) and field-programmable gate arrays (FPGAs), for specific functions. And the choice of CPU or accelerator changes with industry trends, an no trend has been more disruptive than Artificial intelligence (AI).

AI is transforming how the industry envisions compute. It demands exponential increases in performance per watt, from the largest cloud servers to the smallest embedded devices. This is driving new dynamics in scale, efficiency, flexibility and support for an ever-changing, open-source first, software ecosystem. As a result, the entire industry, from silicon to service providers, is looking for unique solutions that often includes different architectures.

The evolution of compute

In the early years of computing, x86 was the architecture of choice, developed by Intel and advanced by both AMD and Intel. The two companies eventually began working together in 2024 on future ISA enhancements to ensure forward compatibility and software enablement. While x86 remains the dominant architecture for PCs and general-purpose servers, it now coexists with a growing ecosystem of RISC (reduced instruction set computer) architectures, often within the same system or SoC. Many x86 SoCs integrate auxiliary RISC cores for security, AI, and power management. One of the key advantages of the x86 architecture is that most PC and server applications were designed for it, providing a legacy of software compatibility. The x86 architecture is also used in many embedded applications, but on a much smaller scale than other, more power-efficient architectures.

The leading processing architecture in terms of both applications and volume is Arm. Arm is the primary architecture for mobile devices, consumer applications/IoT, automotive, and pretty much everything else. While the Arm architecture was originally attractive because of its small size and performance efficiency, it now boasts the largest hardware and software ecosystem.

Arm initially displaced earlier embedded CPU architectures like MIPS and Motorola’s 68k and 88k CPUs. During the 1990s and early 2000s, Arm became the leading RISC architecture for embedded processing in applications ranging from wireless controllers to the functional units for specific processing in everything from custom application-specific integrated circuits (ASICs) to x86 processors. By the late 2000s, Arm displaced many other architectures like SPARC and PowerPC used in data center applications like networking and storage. Over the past decade, Arm has resolved many software compatibility challenges, enabling it to emerge as a credible x86 alternative for PCs and servers.

The Arm architecture now powers all Apple PCs, a growing number of Windows PCs, many server processors from Ampere, Fujitsu, Huawei, Nvidia and all of the custom processors developed by hyperscale service providers, including Alibaba, Amazon, Google, Meta, Microsoft and Tencent. By comparison, between 250 million and 300 million x86 processors were shipped in 2024, some with embedded RISC cores, while an estimated 29 billion Arm processors were shipped with an increasing share in cloud and data center applications.

The third processor architecture is RISC-V, an open-source ISA that anyone can use and modify. While RISC-V is being explored for everything from microcontrollers (MCUs) to AI accelerators, most of the roughly 1 billion cores shipped in 2024 were deeply embedded implementations. RISC-V cores are used for specific MCU-like functions in processors from both the largest x86 and Arm processor vendors, Intel and Qualcomm, respectively. However, it also competes with other CPU and DSP architectures, such as Arc from Synopsys, Tensilica from Cadence and MIPS. And while there is tremendous interest in the RISC-V architecture, the software tools and support lag Arm and x86. RISC-V is very much like Arm in the early days, when it was competing with MIPS and Motorola, it is still in the process of building out an ecosystem and native software support. However, RISC-V’s open licensing allows full customization at the ISA level, making it attractive for custom embedded functions.

Other architectures continue to exist, though in more limited applications. Power is an evolution of the PowerPC architecture for high-performance mainframes and is still under development and in use by IBM. The SPARC architecture developed by Sun Microsystems is still used in some servers and space applications. And MIPS is still used in some MCU applications. Even in these niches, it’s increasingly common to see heterogeneous systems combining multiple architectures.

Shift to multiarchitecture

One of the most recent examples of leveraging multiple CPU architectures in a single solution is the L2600 family of edge AI SoCs from Synaptics. While Arm is the primary architecture used throughout the SoC, it also includes the RISC-V-based Coral NPU developed by Google for AI processing. According to Synaptics, the reason for the dual architecture strategy is that Linux just runs on Arm, while RISC-V offers an open-source solution that may overcome the fragmentation among the different NPUs used in edge device SoCs today.

Synaptics Astra SL2610 using Arm cores and the Coral RISC-V NPU

Synaptics

Every company and architecture is evolving rapidly to meet the demands of the AI era. The RISC-V hardware and software ecosystem continues to develop. AMD and Intel have begun developing different x86 CPU cores for various performance levels, offering more SoC configurations for servers, and offering some level of customization for large customers.

Arm has added complete, pre-validated compute subsystems (CSS) to its broad portfolio of CPU cores, GPU cores, and system IP, and is building an industry-wide chiplet ecosystem through Arm Total Design to support broader chiplet adoption and the creation of more heterogeneous compute solutions. In addition, many of the industry leaders in the Arm ecosystem continue to innovate with custom Arm-compatible CPU designs that address the need for the highest levels of performance efficiency for specific applications. Even the resulting SoCs often use a mixture of custom and standard Arm CPU cores.

The future is heterogeneous

As the semiconductor industry strives to meet the performance efficiency demands of AI and transitions to chiplet-based future processors and SoCs, the use of multiple CPU architectures within the same chip design is likely to become even more common. While chiplets are primarily used in high-end computer applications today, they will eventually reach embedded applications. In the AI and chiplet era, the question is no longer which CPU architecture will win, but how they will work together.